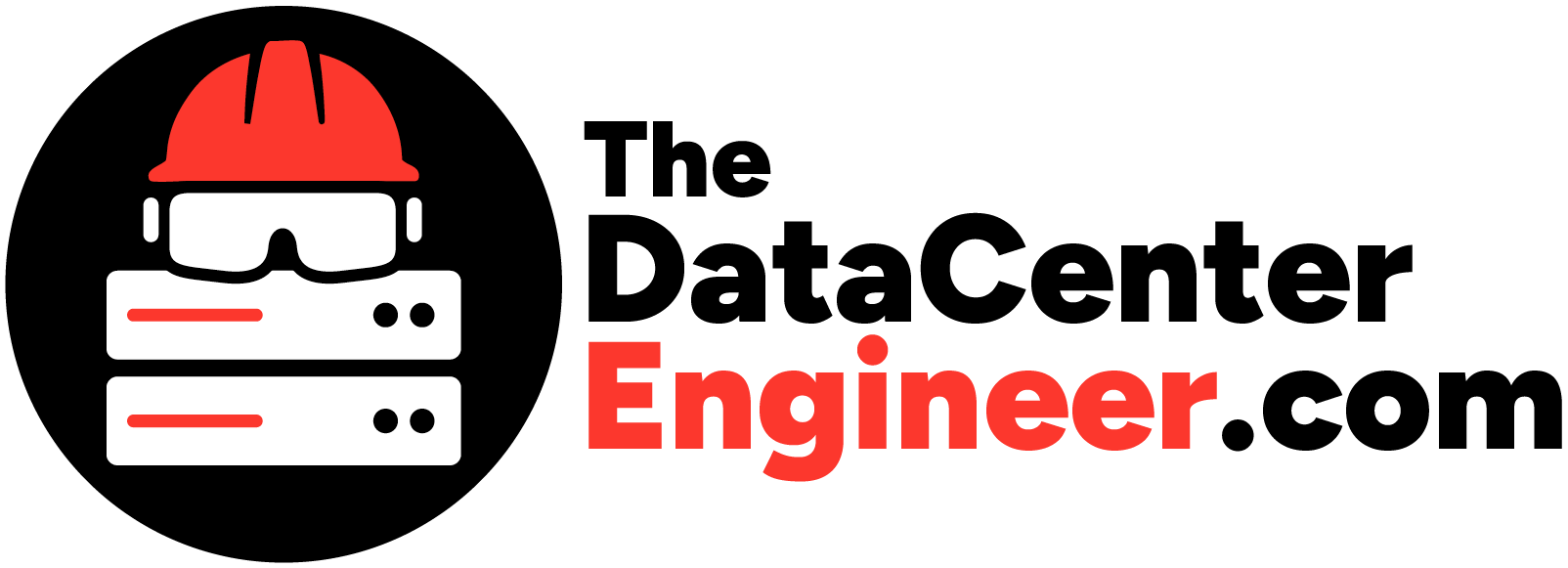

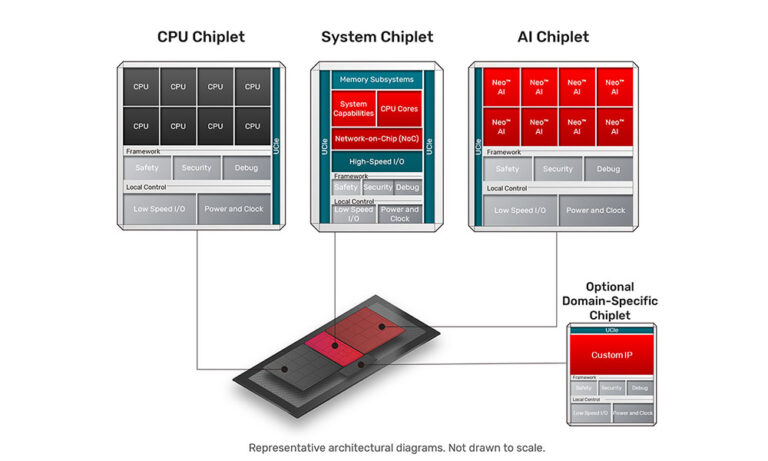

Cadence has announced its Chiplet Spec-to-Packaged Parts ecosystem to reduce engineering complexity and shorten time to market for customers developing chiplets for physical AI, data center, and high-performance computing (HPC) applications. Cadence says the initiative centers on the Cadence Physical AI chiplet platform and provides access to pre-integrated, pre-validated third-party intellectual property (IP) through a partner ecosystem.

Cadence reports that initial IP partners include Arm, Arteris, eMemory, M31 Technology, Silicon Creations, and Trilinear Technologies, with proteanTecs joining as a silicon analytics partner. Cadence also says it is collaborating with Samsung Foundry on a silicon prototype demonstration of the Cadence Physical AI chiplet platform, including pre-integrated partner IP on the Samsung Foundry SF5A process.

The company says it has built spec-driven automation to generate chiplet framework architectures that combine Cadence IP and third-party IP with chiplet management, security, and safety features, supported by software. Cadence says the generated electronic design automation (EDA) tool flow supports simulation with the Cadence Xcelium Logic Simulator and emulation with the Cadence Palladium Z3 Enterprise Emulation Platform, while the physical design flow uses real-time feedback to improve place-and-route cycles.

Cadence says the chiplet architectures are standards-compliant, including adherence to the Arm Chiplet System Architecture and future Open Compute Project (OCP) Foundational Chiplet System Architecture. For die-to-die connectivity, Cadence points to its Universal Chiplet Interconnect Express (UCIe) IP, and it lists protocol IP support for LPDDR6 and LPDDR5X, DDR5-MRDIMM, PCI Express 7.0, and HBM4 for standards-based I/O and memory chiplets targeting data center, cloud, and HPC deployments.

Cadence also reports that an earlier prototype of its base system chiplet, part of the Cadence Physical AI chiplet platform, has been fully silicon validated and incorporates the Cadence chiplet framework, UCIe 32G, and LPDDR5X IP.

Source: Cadence