Kioxia Corporation has announced development of highly stackable oxide-semiconductor channel transistors, aiming to enable high-density, low-power three-dimensional dynamic random access memory (3D DRAM) for use in data centers and related high-performance computing infrastructure. Kioxia showcased this technology at the IEEE International Electron Devices Meeting (IEDM) in San Francisco, USA, on December 10. The company says the technology addresses limitations of current dynamic random access memory (DRAM) in terms of scaling and power consumption, specifically for applications requiring increased capacity and efficiency, such as AI servers and data center equipment.

According to Kioxia, traditional DRAM faces restrictions due to the physical limitations of memory cell miniaturization and higher manufacturing costs associated with single-crystal silicon channels in stacked architectures. As DRAM capacities increase, power demands for cell refresh also rise, which can challenge the operational efficiency of large-scale data center environments.

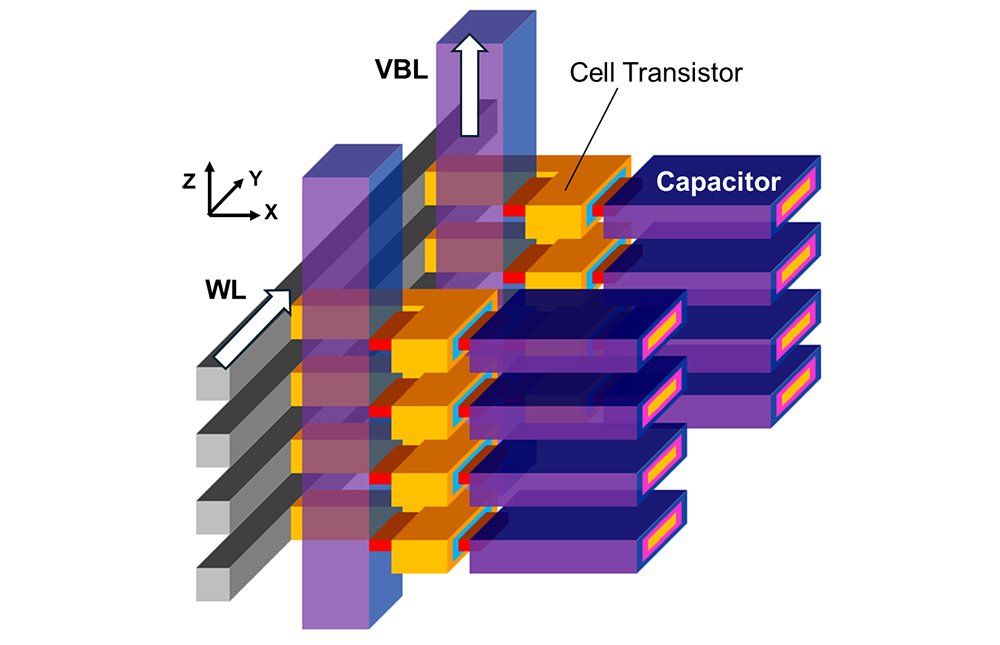

Kioxia presented its oxide-semiconductor channel transistor DRAM (OCTRAM) that leverages vertical transistors made from oxide-semiconductors. In the latest advancement, the company demonstrated a technology that enables eight-layer stacking of OCTRAM transistors. This process involves stacking mature silicon-oxide and silicon-nitride films, followed by replacing the silicon-nitride with an indium gallium zinc oxide (InGaZnO) layer. This creates simultaneous vertical layers of horizontally stacked transistors, facilitating both scaling and high-density integration.

Kioxia claims that this structure allows for significant cost reduction in manufacturing 3D-stacked DRAM. It reports the vertical transistors display high on-current performance (>30 μA) and ultra-low off-current characteristics (<1 aA, or 10-18 A). These properties can reduce refresh power requirements—a critical factor for hyperscale operators and colocation providers managing power budgets in dense server deployments.

The company reports that it has fabricated and verified operation of an 8-layer stack of horizontal transistors, confirming the functionality of the proposed architecture within a laboratory setting. Kioxia notes ongoing research and development intended to move these advancements toward deployment in real-world 3D DRAM products focused on large-scale data processing and AI workloads common in data center technology.

Source: Kioxia