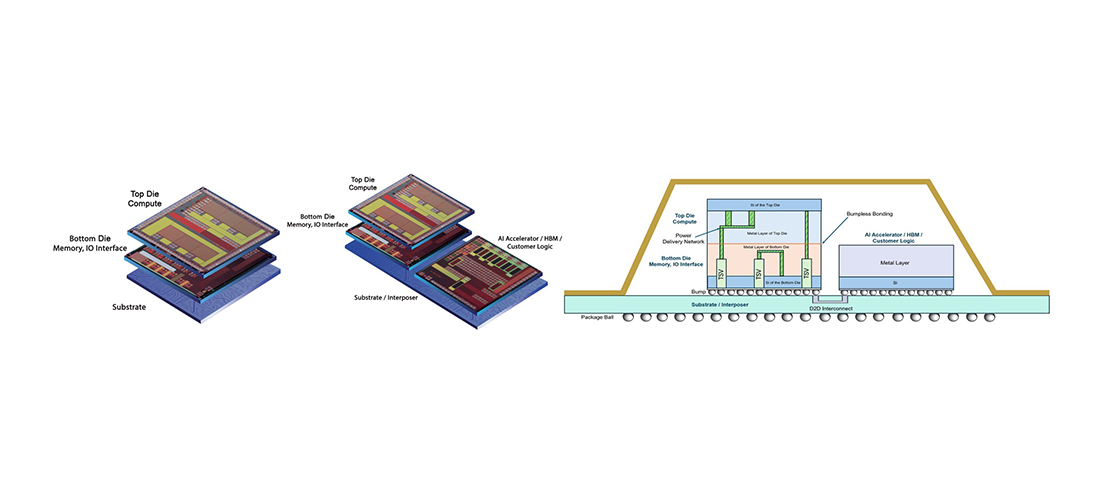

Socionext has announced that its portfolio now includes production-ready three-dimensional integrated circuit (3DIC) solutions targeted at data center, artificial intelligence (AI), and high-performance computing (HPC) applications. The company reports that its expanded capability covers chiplet integration and advanced packaging, specifically chiplets, two-and-a-half-dimensional (2.5D), 3D, and 5.5D configurations.

Socionext states it has taped out a packaged device using Taiwan Semiconductor Manufacturing Company (TSMC) System on Integrated Chips Extended (SoIC-X) technology. This design combines a 3 nanometer (nm) compute die and a 5 nm input–output (I/O) die in a face-to-face (F2F) 3D stack, with the aim of minimizing interconnect distances. According to Socionext, this configuration reduces signal latency and power consumption when compared to traditional two-dimensional (2D) and 2.5D designs.

The 3DIC design process makes use of Socionext’s prior experience in 2.5D architectures. By stacking chip components vertically, 3DICs deliver several potential benefits: the ability to integrate different technology nodes (such as 3 nm, 5 nm, or 7 nm) and chip functions (logic, memory, interface) into a single package; increased functional density in a smaller footprint; improved bandwidth and latency from shorter, wider die-to-die connections; and lower power requirements thanks to more compact, lower impedance interconnects. Socionext claims this approach is well-suited for high-density server environments, data centers, and space-constrained consumer devices.

The company states that combining 3DIC and 5.5D packaging will further support heterogeneous integration, allowing multiple wafer technologies and functions to coexist in a unified system. Socionext identifies data center, AI, and consumer device platforms as key targets for ongoing development of its 3DIC and advanced packaging offerings.

“Socionext’s extensive experience in SoC design and our collaboration with TSMC position us at the forefront of next-generation SoC development,” said Rajinder Cheema, CTO and Executive Vice President at Socionext.

Source: Socionext